Cadence Xcelium Parallel Logic Simulation is the first production-ready third generation multi-core simulator. When compared with the previous simulation engines, Cadence's Xcelium Parallel Logic Simulation achieves 2x performance for single core and 5x performance for multi-cores. The simulator was tested with its implementation into different applications like mobile, automotive, IoT, mobile, consumer, graphics and server.

Read more: Amazon EC2 F1 for custom hardware acceleration

The following are the benefits of Xcelium simulator for accelerating a system development.

Multi-core engine designed for fast SoC simulation:

It analyzes the design of the system and selects the best configuration for the best performance. The speed of different simulations is improved when compared to the preceding simulators - Register-Transfer Level (RTL) simulation by 3x, Gate-Level Simulation (GLS) by 5x and Design For Test (DFT) by 10x.

Single-core engine redesigned for fast IP simulation:

When compared to Cadence Incisive Enterprise Simulator, the speed of Xcelium simulator has been observed twice improved.

Enhancement in verification:

Provides enhanced exclusion flow and parallel multi-core performance, which results in the reduction of time for verification.

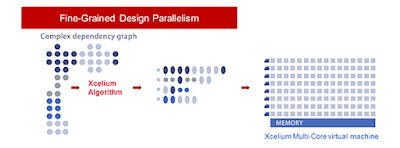

When the second generation simulators take days and weeks for certain simulations, the third generation multi-core provides Xcelium simulator provide fine-grained design parallelism that completes the simulations within hours.

The elaboration process of the third generation simulator is capable of analysing the design graph of every available design. After the analysis it maps the design to the optimal number of cores to achieve maximum speed out the simulator. On the other hand, the developers can modify the number of cores from command line.

Read more: Amazon EC2 F1 for custom hardware acceleration

The following are the benefits of Xcelium simulator for accelerating a system development.

Multi-core engine designed for fast SoC simulation:

It analyzes the design of the system and selects the best configuration for the best performance. The speed of different simulations is improved when compared to the preceding simulators - Register-Transfer Level (RTL) simulation by 3x, Gate-Level Simulation (GLS) by 5x and Design For Test (DFT) by 10x.

Single-core engine redesigned for fast IP simulation:

When compared to Cadence Incisive Enterprise Simulator, the speed of Xcelium simulator has been observed twice improved.

Enhancement in verification:

Provides enhanced exclusion flow and parallel multi-core performance, which results in the reduction of time for verification.

When the second generation simulators take days and weeks for certain simulations, the third generation multi-core provides Xcelium simulator provide fine-grained design parallelism that completes the simulations within hours.

|

| Fine-grained Design Parallelism |

The Xcelium simulator further extends innovation within the Cadence Verification Suite, which is comprised of best-in-class core engines, verification fabric technologies, and solutions that increase design quality and throughput, thus fulfilling verification requirements for a wide variety of use cases and vertical segments.Source: Cadence

0 comments:

Post a Comment